We all know that a gate is a digital logic circuit that, in aggregate, can perform simple logical operations on data. In this post, we will discuss the modeling of the NAND gate from top-down and bottom-up. The following figure shows a basic NAND gate, Gate Level Modeling, Data Flow Modeling, Behavioural Modeling, RTL Simulation, and Truth Table of NAND

NAND Gate

Nand Gate symbol

Nand Gate is a Universal Gate. Nand Gate has two inputs A, B and a single output Y. When both inputs are 0 0 output is 1 when one input is 0 and another input is 1 then output is 1 when one input is 1 and another input is 0 then the output is 1 and when both inputs are 1 the output will be 0

Input A | Input B | Output y |

0 | 0 | 1 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 0 |

Truth Table

Gate Level Modeling

Gate Level Modeling is used to build a lower level circuit by using combinational elements AND and OR. In Gate Level Modeling it is one relationship. Gate level modelling is used to design low-level models such as Multiplexer, Half Adder etc.

Gate-level modeling allows us to design any digital logic circuit using basic logic gates. If you know the gate-level circuit representation of any sensible circuit, you can easily compose its Verilog code using this modeling style. Verilog supports encoding circuits using sensible gateways as pre-defined elements. These primitives are simple instructions that the producer understands. For example, the command is available for use AND intelligence.

module Nand_Gate_Gate_Level(a,b,y);input a,b;output y;nand (y,a,b);endmodule

Data Flow Modeling

Compared to gate-level modeling, data flow modeling is a high level of inaccessibility. That is to say, we do not need to know the complexity of a circuit. This helps as modeling at the gate level becomes more difficult for large circuits.

Data flow modeling is therefore a significant way to use design. All we need to know is the Boolean logic equation of the circuit breaker according to its input. We use continuous assignments to simulate data flow across multiple designs. Ongoing activities are done using the keyword assigned.

The Boolean number for the NAND gate is Y = (A.B) ’or ~ (A & B).

Data Flow modelling is the same as the Gate Level Modeling the difference is that instead of using directly in data flow we use operations such as & (Bit-Wise AND), * (Multiply), % (Modulus), + (Plus), - (Minus) && (Logical AND) etc. Verilog provides 30 different types of Operators. It is used to describe combinational circuits.

module Nand_Gate_Data_Flow(a,b,y);input a,b;output y;assign y = ~(a&b);endmodule

Test Bench

The file to be included and the name of the module change, but the basic structure of the testbench remains the same in all three modeling styles. We have an exciting guide to writing a test bench in Verilog that you may find useful as well.

The code shown below is the test bench for NAND Gate. It is used to give values for Input of NAND Gate. Here a=0; b=0; represent the values of input at A and B. #100 describes the wait time. So that we can get a clear waveform in RTL simulation

module Nand_Gate_test;// Inputsreg a;reg b;// Outputswire y;// Instantiate the Unit Under Test (UUT)Nand_Gate uut (.a(a),.b(b),.y(y));initial begin// Initialize Inputsa=0;b=0;#100 a=0;b=1;#100 a=1;b=0;#100 a=1;b=1;#100;// Add stimulus hereendendmodule

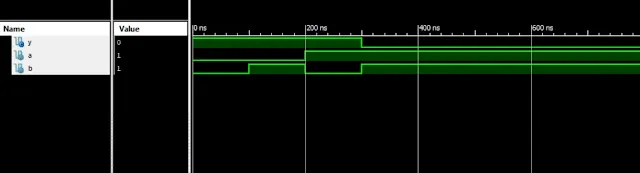

RTL Simulation

Here we represent Register Transfer Level (RTL) For NAND Gate for both Data Level and Data Flow modelling.

It clearly shows that whenever both inputs are high, the output is low or the output is high.

By checking the above waveform we can determine whether our waveform is right or wrong by comparing it with the truth table given above. This waveform has to match with the same truth table of NAND Gate.

Read Also